**Developer Note**

# Apple Logic Board Design LPX-40

**Developer Note** © Apple Computer, Inc. 1996 Apple Computer, Inc.© 1996 Apple Computer, Inc.

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc., except to make a backup copy of any documentation provided on CD-ROM. Printed in the United States of America.

The Apple logo is a trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist application developers to develop applications only for Apple-labeled or Apple-licensed computers.

Every effort has been made to ensure that the information in this manual is accurate. Apple is not responsible for printing or clerical errors.

Apple Computer, Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010

Apple, the Apple logo, AppleLink, Apple SuperDrive, GeoPort, LaserWriter, LocalTalk, Mac, Macintosh, Performa, PlainTalk, PowerBook, and Power Macintosh are trademarks of Apple Computer, Inc., registered in the United States and other countries.

Adobe Illustrator and PostScript are trademarks of Adobe Systems Incorporated, which may be registered in certain jurisdictions.

Helvetica and Palatino are registered trademarks of Linotype Company. The word SRS is a registered trademark of SRS Labs, Inc.

ITC Zapf Dingbats is a registered trademark of International Typeface Corporation.

PowerPC is a trademark of International Business Machines Corporation, used under license therefrom.

Simultaneously published in the United States and Canada.

# LIMITED WARRANTY ON MEDIA AND REPLACEMENT

If you discover physical defects in the manual or in the media on which a software product is distributed, ADC will replace the media or manual at no charge to you provided you return the item to be replaced with proof of purchase to ADC.

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# Contents

Figures and Tables vii

| About This Note ix                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contents of This Note ix<br>Supplemental Reference Documents ix<br>The <i>Apple Developer Catalog x</i><br>Apple Developer World Web Site x<br>Conventions and Abbreviations x<br>Typographical Conventions xi<br>Standard Abbreviations xi                                               |

| Introduction 1                                                                                                                                                                                                                                                                            |

| Summary of Features2Comparison With Power Macintosh 6400 Computer3Compatibility Issues4MFM Floppy Drive5DRAM Expansion5DRAM DIMM Dimensions6Cache Expansion6                                                                                                                              |

| ATA (IDE) Hard Disk and ATAPI CD-ROM Drive 6<br>PS/2 Keyboard Support 6<br>Video Display RAM 6                                                                                                                                                                                            |

| Architecture 9                                                                                                                                                                                                                                                                            |

| Block Diagram and Main ICs 10<br>Main Processor 10<br>PowerPC 603e Microprocessor 10<br>PowerPC 604e Microprocessor 10<br>Memory Subsystem 11<br>RAM 11<br>ROM 11<br>Second-Level Cache (Optional) 11<br>System RAM 13<br>Custom ICs 13<br>PSX IC 13<br>O'Hare IC 15<br>AWACS Sound IC 15 |

|                                                                                                                                                                                                                                                                                           |

CudaLite IC 16 ATI 264VT-A4S2 IC 16 Display RAM DIMM 16

## Chapter 3

## I/O Features 19

| Board Layout 20                  |

|----------------------------------|

| Serial I/O Ports 22              |

| Apple Printer and Modem Ports 22 |

| PS/2 Keyboard and Mouse Ports 24 |

| ADB Port 26                      |

| Apple ADB Keyboard 27            |

| Disk Drives 28                   |

| Floppy Disk Drives 28            |

| GCR Floppy Disk Drive 28         |

| MFM Floppy Disk Drive 29         |

| ATA (IDE) Hard Disk 30           |

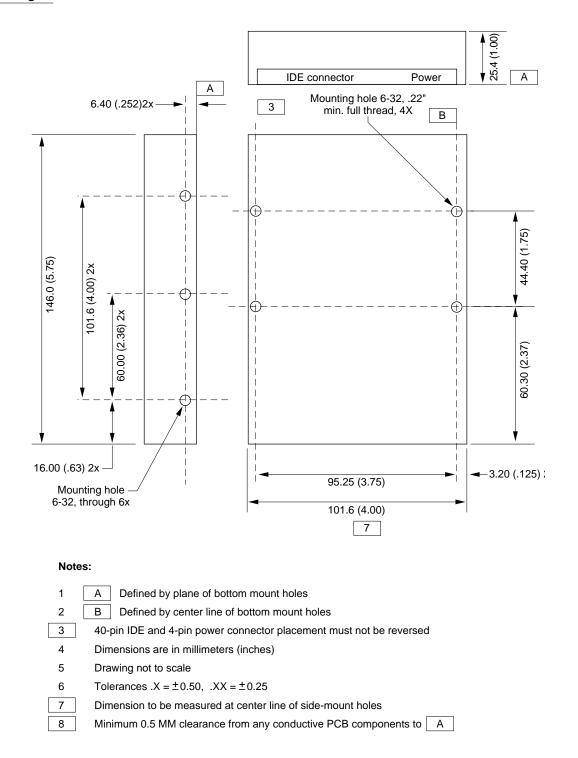

| Hard Disk Specifications 30      |

| Hard Disk Connectors 32          |

| Pin Assignments 32               |

| ATA (IDE) Signal Descriptions 33 |

| CD-ROM Drive 33                  |

| SCSI Bus 34                      |

| SCSI Connector 34                |

| SCSI Bus Termination 35          |

| Sound 35                         |

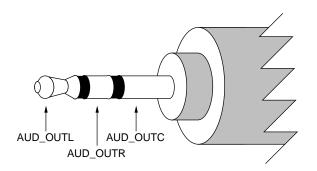

| Sound Output 35                  |

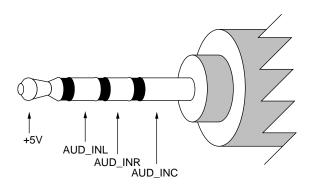

| Sound Input 36                   |

| Sound Input Specifications 37    |

| Digitizing Sound 38              |

| Sound Modes 38                   |

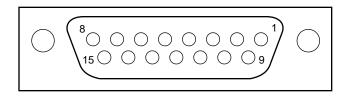

| Built-in Video 38                |

| Video Connectors 39              |

| Video Display Sense Codes 41     |

| Video Display Resolution 44      |

| Power Supply 44                  |

| Power Specifications 45          |

| Power Supply Connectors 46       |

| Chapter 4 | Expansion Features |  |

|-----------|--------------------|--|

|           | DRAM DIMMs 48      |  |

|           |                    |  |

RAM DIMMs48DRAM DIMM Connectors50RAM Address Multiplexing53

47

|           | RAM Devices54RAM Refresh54RAM DIMM Dimensions54Second-Level Cache DIMM56Video RAM58Video RAM DIMM Card61PCI Expansion Slot62                                                                                                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5 | MFM Floppy Disk Device Driver 65                                                                                                                                                                                                                                                      |

|           | About the MFM Floppy Disk Driver 66<br>Using the MFM Floppy Disk Driver 67<br>MFM Floppy Driver API Reference 67<br>Read and Write Prime Routines 67<br>Control Calls 69<br>Status Calls 77<br>Copy Protection and MFM Floppy Disk Controllers 80<br>Floppy Drive Gestalt Selector 81 |

Index 83

# Figures and Tables

| Chapter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Table 1-1                                                                                                                                                                                                                                                                                                                                                                                                             | Comparison with the Macintosh Performa 6400 series computer 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Table 1-2                                                                                                                                                                                                                                                                                                                                                                                                             | Gestalt values for Apple Logic Board Design LPX-40 configurations 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 2 | Architecture                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

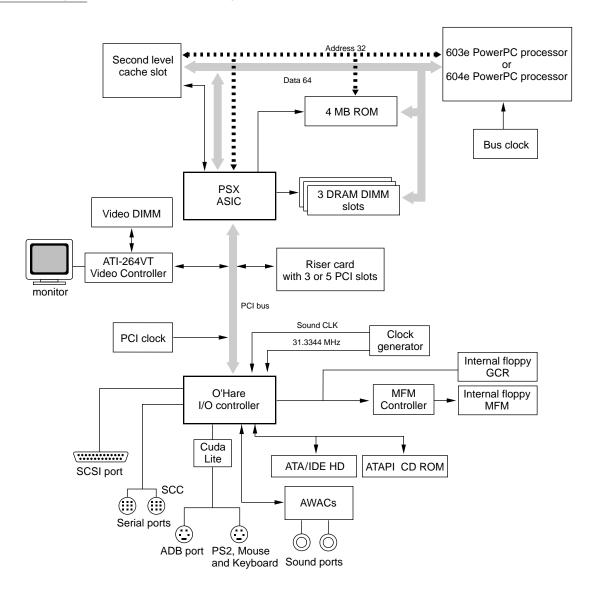

|           | Figure 2-1                                                                                                                                                                                                                                                                                                                                                                                                            | System block diagram 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapter 3 | I/O Features                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           | Figure 3-1<br>Figure 3-2<br>Figure 3-3<br>Figure 3-4<br>Figure 3-5<br>Figure 3-6<br>Figure 3-7<br>Figure 3-8<br>Figure 3-9<br>Table 3-1<br>Table 3-2<br>Table 3-3<br>Table 3-3<br>Table 3-4<br>Table 3-5<br>Table 3-6<br>Table 3-7<br>Table 3-7<br>Table 3-8<br>Table 3-9<br>Table 3-10<br>Table 3-11<br>Table 3-12<br>Table 3-13<br>Table 3-14<br>Table 3-15<br>Table 3-16<br>Table 3-17<br>Table 3-18<br>Table 3-19 | Apple Logic Board Design LPX-40 connector layout20Serial port sockets22ADB handler ID=2 key maps and key codes25ADB handler ID=3 key maps and key codes26Maximum dimensions of the hard disk31Mini-phono jack for sound output36Mini-phono microphone sound-input jack38Macintosh 15-pin external monitor connector39SVGA 15-pin external monitor connector40Connectors on the Apple Logic Board Design LPX-4021Serial port signals23PS/2 port signals24ADB connector pin assignments27Reset and NMI key combinations28Pin assignments on the GCR floppy disk connector29Pin assignments on the ATA (IDE) hard disk connector32Signals on the ATA (IDE) hard disk connector33Pin assignments for the SCSI connectors34Signal assignments for the sound output connector36Signal assignments for the sound-nput jack37Pin assignments for the SVGA external monitor connector40SVGA to Macintosh video adapter pin assignments41Video display sense codes42Maximum pixel depths for resolution setting44DC power specifications for a 200-watt power supply45Pin assignments for the power supply connectors46 |

| Chapter 4 | Expansion Fea          | nsion Features 47                                                                          |  |  |

|-----------|------------------------|--------------------------------------------------------------------------------------------|--|--|

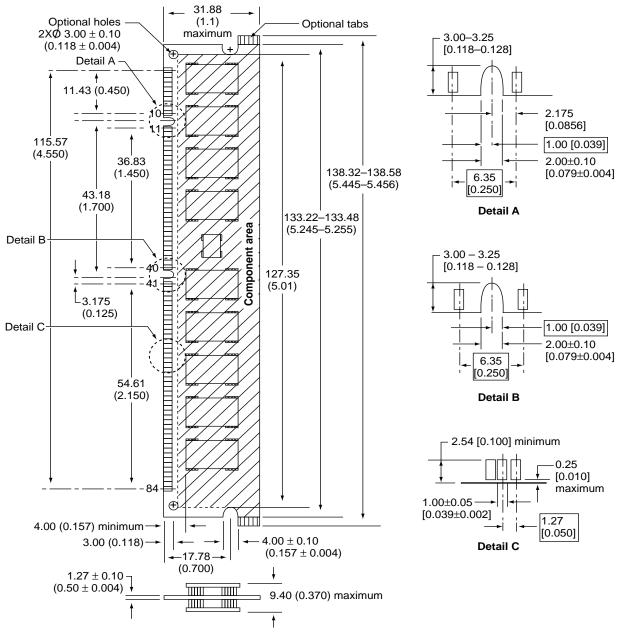

|           | Figure 4-1             | Dimensions of the RAM DIMM 55                                                              |  |  |

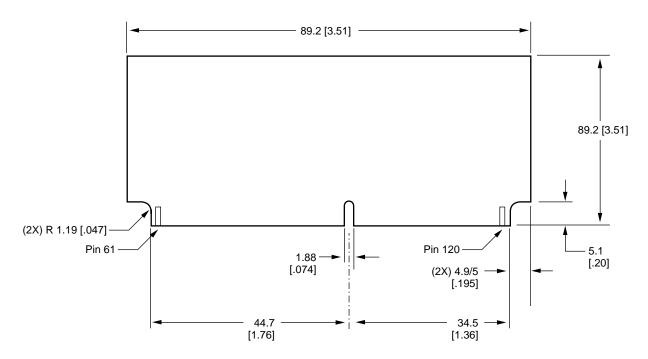

|           | Figure 4-2             | Video DIMM card dimensions 62                                                              |  |  |

|           | Table 4-1              | DRAM DIMM configurations supported in DIMM slot 1 48                                       |  |  |

|           | Table 4-2              | DRAM DIMM configurations supported in DIMM slots 2 and 3 49                                |  |  |

|           | Table 4-3              | Pin assignments on the 3.3 V unbuffered EDO DRAM DIMM connectors 50                        |  |  |

|           | Table 4-4              | RAM DIMM signals 53                                                                        |  |  |

|           | Table 4-5              | Address multiplexing modes for various DRAM devices 53                                     |  |  |

|           | Table 4-6              | Address multiplexing in noninterleaved banks 54                                            |  |  |

|           | Table 4-7              | Pin and signal assignments for the L2 cache DIMM<br>connector 56                           |  |  |

|           | Table 4-8              | Signal descriptions for L2 cache DIMM connector 57                                         |  |  |

|           | Table 4-9              | Pin and signal assignments on the 120-pin video DIMM connector 59                          |  |  |

|           | Table 4-10             | PCI signals 63                                                                             |  |  |

| Chapter 5 | MFM Floppy D           | Disk Device Driver 65                                                                      |  |  |

|           | Figure 5-1             | Relationship between clockBitsBuffer and dataBuffer 74                                     |  |  |

|           | Table 5-1<br>Table 5-2 | Read and write prime routine result codes 68<br>Floppy disk drive attributes bit values 81 |  |  |

# About This Note

This developer note describes the Apple Logic Board Design LPX-40. It is intended to help experienced Macintosh hardware and software developers design compatible products. If you are unfamiliar with Macintosh computers or would simply like more technical information, you may wish to read the related technical documents listed in the section "Supplemental Reference Documents."

# Contents of This Note

The information is arranged in five chapters and an index.

- Chapter 1, "Introduction," gives a summary of the features of the Apple Logic Board Design LPX-40 and discusses issues related to compatibility with other Macintosh computer software and hardware.

- Chapter 2, "Architecture," describes the organization of the logic board. This chapter includes a block diagram and descriptions of the main components of the logic board.

- Chapter 3, "I/O Features," describes the built-in input/output (I/O) device interfaces and the external I/O ports. It also describes the built-in video support for external video monitors.

- Chapter 4, "Expansion Features," describes the expansion slots on the Apple Logic Board Design LPX-40. This chapter provides guidelines for designing cards for the I/O expansion slot and brief descriptions of the expansion modules for the other slots.

- Chapter 5, "MFM Floppy Disk Device Driver," gives the program interface for the system software and the driver that supports systems configured with an MFM internal floppy disk drive.

## Supplemental Reference Documents

For a description of the version of the Mac OS that supports the Apple Logic Board Design LPX-40, developers should refer to Technote 1050.

Developers should have the relevant books of the *Inside Macintosh* series. You should also have *Designing PCI Cards and Drivers for Power Macintosh Computers*. These books are available in technical bookstores and through the *Apple Developer Catalog*. You should also have the *ATA Device Software Guide* if you plan to develop software utilities or drivers for ATA or ATAPI devices.

## The Apple Developer Catalog

The *Apple Developer Catalog* (ADC) is Apple Computer's worldwide source for hundreds of development tools, technical resources, training products, and information for anyone interested in developing applications on Apple computer platforms. Customers receive the *Apple Developer Catalog* featuring all current versions of Apple development tools and the most popular third-party development tools. ADC offers convenient payment and shipping options, including site licensing.

To order products or to request a complimentary copy of the *Apple Developer Catalog*, contact

Apple Developer Catalog Apple Computer, Inc. P.O. Box 319 Buffalo, NY 14207-0319

| Telephone | 1-800-282-2732 (United States)<br>1-800-637-0029 (Canada)<br>716-871-6555 (International) |

|-----------|-------------------------------------------------------------------------------------------|

| Fax       | 716-871-6511                                                                              |

| AppleLink | ORDER.ADC                                                                                 |

| Internet  | http://www.devcatalog.apple.com                                                           |

# Apple Developer World Web Site

The Apple Developer World web site is the one-stop source for finding technical and marketing information specifically for developing successful Macintosh-compatible software and hardware products. Developer World is dedicated to providing developers with up-to-date Apple documentation for existing and emerging Macintosh technologies. Developer World can be reached at http://www.devworld.apple.com.

# Conventions and Abbreviations

This developer note uses the following typographical conventions and abbreviations.

## Typographical Conventions

New terms appear in **boldface** where they are first defined.

Computer-language text—any text that is literally the same as it appears in computer input or output—appears in Courier font.

Hexadecimal numbers are preceded by a dollar sign (\$). For example, the hexadecimal equivalent of decimal 16 is written as \$10.

#### Note

A note like this contains information that is interesting but not essential for an understanding of the text.  $\blacklozenge$

#### IMPORTANT

A note like this contains important information that you should read before proceeding.  $\blacktriangle$

## Standard Abbreviations

When unusual abbreviations appear in this book, the corresponding terms are also spelled out. Standard units of measure and other widely used abbreviations are not spelled out. Here are the standard units of measure used in this developer note:

| А   | amperes   | mA   | milliamperes |

|-----|-----------|------|--------------|

| dB  | decibels  | μA   | microamperes |

| GB  | gigabytes | MB   | megabytes    |

| Hz  | hertz     | MHz  | megahertz    |

| in. | inches    | mm   | millimeters  |

| k   | 1000      | ms   | milliseconds |

| Κ   | 1024      | μs   | microseconds |

| KB  | kilobytes | ns   | nanoseconds  |

| kg  | kilograms | Ω    | ohms         |

| kHz | kilohertz | sec. | seconds      |

| kΩ  | kilohms   | V    | volts        |

| lb. | pounds    | W    | watts        |

Here are other abbreviations that may used in this developer note:

| \$ <i>n</i> | hexadecimal value n                              |

|-------------|--------------------------------------------------|

| AC          | alternating current                              |

| ADB         | Apple Desktop Bus                                |

| AV          | audiovisual                                      |

| AWACS       | audio waveform amplifier and converter for sound |

| CD-ROM      | compact disk read-only memory                    |

| CLUT   | color lookup table                                                                                                        |

|--------|---------------------------------------------------------------------------------------------------------------------------|

| DAC    | digital to analog converter                                                                                               |

| DAV    | digital audio video                                                                                                       |

| DDC    | display data channel                                                                                                      |

| DESC   | digital video decoder and scaler                                                                                          |

| DIMM   | dual inline memory module                                                                                                 |

| DMA    | dynamic memory access                                                                                                     |

| DRAM   | dynamic random-access memory                                                                                              |

| DVA    | digital video application                                                                                                 |

| EMI    | electromagnetic interference                                                                                              |

| FPU    | floating-point unit                                                                                                       |

| GCR    | group code recording                                                                                                      |

| GIMO   | graphic internal monitor out (for PC compatibility cards)                                                                 |

| IC     | integrated circuit                                                                                                        |

| IDE    | integrated device electronics                                                                                             |

| IIC    | inter-integrated circuit (an internal control bus)                                                                        |

| I/O    | input/output                                                                                                              |

| IR     | infrared                                                                                                                  |

| LS TTL | low-power Schottky TTL (a standard type of device)                                                                        |

| MESH   | Macintosh enhanced SCSI hardware                                                                                          |

| MFM    | modified frequency modulation                                                                                             |

| MMU    | memory management unit                                                                                                    |

| MOS    | metal-oxide semiconductor                                                                                                 |

| NTSC   | National Television Standards Committee (the standard system used for broadcast TV in North America and Japan)            |

| NMI    | nonmaskable interrupt                                                                                                     |

| PAL    | Phase Alternating Line system (the standard for broadcast TV in most of Europe, Africa, South America, and southern Asia) |

| PCI    | Peripheral Component Interconnect                                                                                         |

| PDS    | processor-direct slot                                                                                                     |

| PLL    | phase locked loop                                                                                                         |

| PWM    | pulse-width modulation                                                                                                    |

| RAM    | random-access memory                                                                                                      |

| RGB    | a video signal format with separate red, green, and blue components                                                       |

| RISC   | reduced instruction set computing                                                                                         |

| RMS    | root-mean-square                                                                                                          |

| ROM    | read-only memory                                                                                                          |

| SANE   | Standard Apple Numerics Environment                                                                                       |

## P R E F A C E

| SCSI    | Small Computer System Interface                                                                           |

|---------|-----------------------------------------------------------------------------------------------------------|

| SCC     | serial communications controller                                                                          |

| SECAM   | the standard system used for broadcast TV in France and the former Soviet countries                       |

| SIMM    | single inline memory module                                                                               |

| S-video | a type of video connector that keeps luminance and chrominance separate; also called a Y/C connector      |

| SWIM    | Super Woz Integrated Machine, a custom IC that controls the floppy disk interface                         |

| TTL     | transistor-transistor logic (a standard type of device)                                                   |

| VCR     | video-cassette recorder                                                                                   |

| VLSI    | very large scale integration                                                                              |

| VRAM    | video RAM; used for display buffers                                                                       |

| Y/C     | a type of video connector that keeps luminance and chrominance separate; also called an S-video connector |

| YUV     | a video signal format with separate luminance and chrominance components                                  |

|         |                                                                                                           |

# Introduction

CHAPTER 1

Introduction

The Apple Logic Board Design LPX-40 is a new Power Macintosh logic board that incorporates either a PowerPC<sup>™</sup> 603e or PowerPC 604e microprocessor, a second-level (L2) cache expansion slot, three DRAM expansion slots, three or five Peripheral Component Interconnect (PCI) card expansion slots (with installation of a riser card), standard Macintosh I/O ports, two PS/2 serial ports to support a PS/2 keyboard and mouse, and support for an internal ATAPI CD-ROM drive. The Apple Logic Board Design LPX-40 layout follows the LPX form factor and can be housed in LPX low profile or tower enclosures.

## Summary of Features

Here is a summary of the hardware features of the Apple Logic Board Design LPX-40. Each feature is described more fully later in this note.

- Microprocessor: PowerPC 603e microprocessor running at 160 MHz, 180 MHz, and 200 MHz, or PowerPC 604e microprocessor running at 160 MHz and 200 MHz.

- RAM: 0 MB soldered to the main logic board; expandable to 96 MB using 168-pin JEDEC-standard 3.3 volt unbuffered EDO (extended data out) DIMM (dual inline memory module) devices. Three DIMM slots are provided for DRAM expansion.

- ROM: 4 MB soldered on main logic board; 64-bit ROM data bus width.

- Cache: 256 KB L2 cache on a 160-pin DIMM card (optional).

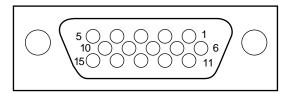

- Macintosh standard 15-pin monitor connector or a 15-pin SVGA connector.

- Video display modes: the LPX-40 logic board provides support for a wide range of displays depending on the amount of video RAM installed. For a complete description of the display modes and pixel resolutions supported by the LPX-40 logic board, see "Built-in Video" beginning on page 38.

- 2D built-in graphics acceleration.

- Sound: 16 bits/channel stereo sound input and output, external rear jack for sound in, rear jack for headphones or amplified stereophonic speakers, and one built-in speaker.

- Hard disks: one internal 3.5-inch IDE hard disk with 1.2 GB or larger capacity; external SCSI port (DB-25) for additional SCSI devices. PIO, singleword DMA, and multiword DMA data transfers are supported.

- CD-ROM drive support: internal 8X-speed ATAPI CD-ROM drive.

- PCI card expansion slots: accepts either three or five 7-inch or 12-inch PCI cards depending on the enclosure and expansion/riser card configuration; available power for the slots is dependent on the enclosure power supply.

- Floppy disk support: one internal 1.4 MB Apple SuperDrive or one internal MFM floppy drive.

- Processor bus: 64-bit wide, 40 MHz, supporting split address and data tenures.

- Standard Macintosh I/O ports: two GeoPort serial ports, sound input and output jacks, a SCSI port, and an ADB port.

#### Introduction

- PC standard I/O ports: two PS/2 serial ports for keyboard and mouse.

- Apple GeoPort: supported on the Macintosh printer and modem serial ports.

- Power switch: support for soft power from keyboard and power switch.

- Voltage switch: allows selection of either 115 for voltages of 100-130 V or 230 for voltages of 200-230 V depending on the voltage that you will be connecting to. The voltage selection must be set manually on the power supply.

- Energy saving: sleep, startup, and shutdown scheduling can be controlled with an Energy Saver control panel.

## Comparison With Power Macintosh 6400 Computer

The LPX-40 main logic board is based on the architecture of the main logic board in the Power Macintosh 5400 and Macintosh Performa 6400 computers. Table 1-1 compares the features of the Apple Logic Board Design LPX-40 with the Macintosh Performa 6400 computer.

| Features        | Macintosh Performa 6400                                                              | Apple Logic Board Design<br>LPX-40                                                                                                               |

|-----------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor type  | PowerPC 603e                                                                         | PowerPC 603e or 604e                                                                                                                             |

| Processor speed | 120 MHz, 160 MHz,<br>180 MHz, 200 MHz                                                | 160 MHz, 180 MHz, and<br>200 MHz                                                                                                                 |

| Cache           | 256 KB L2 cache (optional)                                                           | 256 KB L2 cache (optional)                                                                                                                       |

| Amount of RAM   | 8 MB-136 MB                                                                          | 0 MB-96 MB                                                                                                                                       |

| RAM expansion   | 2 168-pin 5 volt fast-paged<br>mode DIMMs                                            | 3 168-pin 3.3 volt unbuffered<br>EDO DIMMs                                                                                                       |

| Memory bus      | 64 bits, 40 MHz                                                                      | 64 bits, 40 MHz                                                                                                                                  |

| Video RAM       | 1 MB (DRAM)                                                                          | 1 MB expandable to 4 MB<br>(EDO DRAM, SDRAM, or<br>SGRAM depending on logic<br>board configuration)                                              |

| Video input     | Optional card for video input, capture, and overlay                                  | None (third-party PCI cards)                                                                                                                     |

| Video output    | Built-in video supports up<br>to 1024-by-768 pixel<br>resolution at 8 bits per pixel | Depending on the amount<br>of video RAM installed, the<br>built-in video supports up to<br>1280-by-1024 pixel<br>resolution at 16 bits per pixel |

#### Table 1-1 Comparison with the Macintosh Performa 6400 series computer

continued

#### Introduction

|                                |                                                                                           | Annia Logia Doord Dooing                                                                                |

|--------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Features                       | Macintosh Performa 6400                                                                   | Apple Logic Board Design<br>LPX-40                                                                      |

| Graphics<br>acceleration       | None                                                                                      | 2D graphics acceleration                                                                                |

| Sound capabilities             | 8 or 16 bits/channel; stereo<br>in, stereo record, stereo out;<br>SRS surround-sound mode | 8 or 16 bits/channel; stereo<br>in, stereo record, stereo out                                           |

| Remote control                 | Built-in IR receiver for optional TV/FM tuner card                                        | None                                                                                                    |

| Floppy disk drive              | 1, internal (GCR)                                                                         | 1, internal (MFM or GCR)                                                                                |

| ADB ports                      | 1                                                                                         | 1                                                                                                       |

| PS/2 ports                     | None                                                                                      | 2, for PS/2 keyboard and mouse                                                                          |

| Internal hard disk             | 1 (IDE/ATA)                                                                               | Supports 1 (IDE/ATA)                                                                                    |

| Internal CD-ROM                | 1 SCSI                                                                                    | Supports 1 (ATAPI)                                                                                      |

| Internal SCSI<br>expansion bay | 1                                                                                         | None                                                                                                    |

| External SCSI ports            | 1                                                                                         | 1                                                                                                       |

| Expansion slots                | 2 PCI slots for 7-inch cards                                                              | 3 or 5 PCI slots for 7-inch or<br>12-inch PCI cards,<br>depending on the riser card<br>in the enclosure |

| DMA I/O                        | 10 DMA channels                                                                           | 10 DMA channels                                                                                         |

| Serial ports                   | 2, LocalTalk and GeoPort supported                                                        | 2, LocalTalk and GeoPort supported                                                                      |

#### Table 1-1 Comparison with the Macintosh Performa 6400 series computer (continued)

# **Compatibility Issues**

The Apple Logic Board Design LPX-40 incorporates several changes from logic boards found in earlier desktop models. This section describes key issues you should be aware of to ensure that your hardware and software work properly with this new logic board. Some of the topics described here are covered in more detail in later parts of this developer note.

#### CHAPTER 1

#### Introduction

The gestalt values for the various Apple Logic Board Design LPX-40 configurations are listed in Table 1-2.

| Table 1-2 | Gestalt values for Apple Logic Board Design LPX-40 configurations |

|-----------|-------------------------------------------------------------------|

|           |                                                                   |

| Gestalt value | Description of board configuration                                                         |

|---------------|--------------------------------------------------------------------------------------------|

| 511           | Manual-eject MFM floppy drive with soft power                                              |

| 514           | Auto-eject GCR floppy drive with soft power                                                |

| 516           | Manual-eject MFM floppy drive with hard power                                              |

| 517           | Auto-eject GCR floppy drive with hard power                                                |

| 518           | Auto-eject MFM floppy drive with soft power                                                |

| 519           | Auto-eject MFM floppy drive with hard power                                                |

| 518           | Auto-eject GCR floppy drive with hard power<br>Auto-eject MFM floppy drive with soft power |

## MFM Floppy Drive

The Apple Logic Board Design LPX-40 has connectors for MFM (modified frequency modulation) and GCR (group code recording) floppy disk drives.

If the computer that the Apple Logic Board Design LPX-40 is installed in is equipped with an MFM floppy drive, Macintosh application copy protection schemes that rely on the GCR floppy drive, found in all previous Macintosh models, will no longer work with the MFM floppy. In addition, Macintosh disk drive utility programs should incorporate new code for manipulating data on the MFM floppy drive. For additional information about controlling the MFM floppy drive, see Chapter 5, "MFM Floppy Disk Device Driver."

## **DRAM** Expansion

The Apple Logic Board Design LPX-40 requires 168-pin 3.3 volt unbuffered EDO (extended data out) JEDEC-standard DRAM DIMM cards rather than the 168-pin 5 volt fast-page DIMM cards used in the Power Macintosh 5400, 7600, 8500, and 9500 computers and the Macintosh Performa 6400. The connector notches have different offsets to differentiate between device types and to ensure that the correct devices are installed on the logic board. For information about DRAM DIMM configurations supported on the Apple Logic Board Design LPX-40, see "DRAM DIMMs" beginning on page 48 in Chapter 4, "Expansion Features."

The Apple Logic Board Design LPX-40 has three DRAM expansion slots. DRAM expansion slot 1 supports single-bank DIMMs. DRAM expansion slots 2 and 3 support both single-bank and dual-bank DIMMs. No DRAM is soldered on the main logic board.

DRAM DIMM developers should note that the PSX memory controller on the Apple Logic Board Design LPX-40 does not provide support for 4 M by 4 bits with 12-by-10 addressing, 1 M by 16 bits with 12-by-8 addressing, or with 11-by-9 addressing DRAM devices.

Introduction

## **DRAM DIMM Dimensions**

The JEDEC MO-161-B specification shows three possible heights for the 8-byte DIMM. For Macintosh computers, it is recommended that developers use only the shortest of the three: 1.100 inches. Taller DIMMs could put excessive pressure on the DIMM sockets due to possible mechanical interference inside the case.

## Cache Expansion

The Apple Logic Board Design LPX-40 supports an optional 256K second-level DIMM cache card that includes an integrated cache controller. Apple does not support development of third-party cache cards for the Apple Logic Board Design LPX-40. The 160-pin cache expansion slot is the same as the cache slot found in the Power Macintosh 5400 and Macintosh Performa 6400 computer models.

## ATA (IDE) Hard Disk and ATAPI CD-ROM Drive

The interface for the internal hard disk and CD-ROM drive on the Apple Logic Board Design LPX-40 is ATA (IDE) for the hard disk and ATAPI for the CD-ROM, not SCSI. This could cause compatibility problems for disk utility programs. The system software release for computers equipped with the Apple Logic Board Design LPX-40 includes version 3.0 or greater of the ATA Manager and supports PIO, singleword DMA, and multiword DMA data transfers. For more information about the software that controls ATA devices, see the *ATA Device Software Guide*.

## PS/2 Keyboard Support

The Apple Logic Board Design LPX-40 provides two PS/2 serial ports for connection of a PS/2 keyboard and PS/2 mouse. The PS/2 implementation on the Apple Logic Board Design LPX-40 does not support all permutations of PS/2 keyboards and mouse devices. In particular, only two-button mouse devices are supported and only AT-type keyboards are supported.

The PS/2 to ADB conversion protocol, contained in the CudaLite ASIC, only supports PS/2 mouse devices that generate a binary 1 in the sync bit position (bit 3 of the first data byte) of the protocol. If the PS/2 mouse device generates a binary 0 in the sync bit position, the device is not recognized.

PC keyboards that implement XT or RT key codes are not supported. For additional information about PS/2 keyboard and mouse support on the Apple Logic Board Design LPX-40, see "PS/2 Keyboard and Mouse Ports" beginning on page 24.

## Video Display RAM

In addition to 2D QuickDraw graphics acceleration, the Apple Logic Board Design LPX-40 has a new video RAM DIMM expansion implementation. It supports expansion of up to 4 MB of video RAM through a variety of video RAM devices. The Apple Logic

#### Introduction

Board Design LPX-40 also supports DDC (display data channel) plug-and-play monitor identification.

For additional information about video display resolution and video display sense codes supported by the Apple Logic Board Design LPX-40, see "Built-in Video" on page 38. For a description of the new video RAM DIMM connector on the Apple Logic Board Design LPX-40, see "Video RAM" on page 58.

#### CHAPTER 2

Architecture

This chapter describes the architecture of the Apple Logic Board Design LPX-40. It describes the major components of the main logic board: the microprocessor, the custom ICs, and the display RAM.

# Block Diagram and Main ICs

The Apple Logic Board Design LPX-40 can be configured with either the PowerPC 603e or PowerPC 604e microprocessor. The board is designed with many of the custom ICs that are used on the logic board in the Macintosh Performa 6400. Figure 2-1 shows the system block diagram. The architecture of the Apple Logic Board Design LPX-40 is based on two buses: the processor bus and the PCI bus. The processor bus connects the microprocessor, ROM, cache, and memory; the PCI bus connects the video expansion slots and the I/O devices.

### Main Processor

The Apple Logic Board Design LPX-40 can be configured with either a PowerPC 603e or 604e main processor.

#### PowerPC 603e Microprocessor

The PowerPC 603e microprocessor runs at 160, 180, and 200 MHz. The principle features of the PowerPC 603e microprocessor include

- full RISC processing architecture

- parallel processing units: two integer and one floating-point

- a branch manager that can usually implement branches by reloading the incoming instruction queue without using any processing time

- an internal memory management unit (MMU)

- 32 KB of on-chip cache memory (16 KB for data and 16 KB for instructions)

For complete technical details, see the PowerPC 603 RISC Microprocessor User's Manual.

#### PowerPC 604e Microprocessor

The PowerPC 604e microprocessor runs at 160 and 200 MHz. The principle features of the PowerPC 604e microprocessor include

- full RISC processing architecture

- parallel processing units: load-store unit, two integer units, one complex integer unit, and one floating-point unit

- a branch manager that can usually implement branches by reloading the incoming instruction queue without using any processing time

- an internal memory management unit (MMU)

■ 32 KB of on-chip cache memory (16 KB for data and 16 KB for instructions)

For complete technical details, see the PowerPC 604 RISC Microprocessor User's Manual.

## Memory Subsystem

The memory subsystem of the Apple Logic Board Design LPX-40 consists of RAM, ROM, and an optional second-level (L2) cache. The PSX custom IC provides burst mode control to the cache and ROM.

### RAM

There are no DRAM devices soldered on the logic board. Three slots are provided for RAM expansion. 168-pin 3.3 volt unbuffered EDO (extended data out) JEDEC-standard DRAM DIMM cards are required. The maximum supported DRAM is three slots containing 32 MB each for a total of 96 MB. For additional information about the supported DRAM devices, see "DRAM DIMMs" on page 48.

### ROM

The ROM consists of 4 MB of masked ROM soldered to the main logic board.

### Second-Level Cache (Optional)

The optional second-level (L2) cache consists of 256 KB of high-speed RAM on a 160-pin DIMM card, which is plugged into a 160-pin edge connector on the main logic board. For additional information about the second-level cache, see "Second-Level Cache DIMM" on page 56.

CHAPTER 2

#### Architecture

#### Figure 2-1 System block diagram

## System RAM

The Apple Logic Board Design LPX-40 has no DRAM memory soldered on the main logic board. All RAM expansion is provided by 3.3 volt unbuffered EDO DRAM devices on 8-byte JEDEC-standard DIMMs. Three 168-pin DIMM sockets are used for memory expansion. Available DRAM DIMM sizes are 8, 16, and 32 MB. DIMM socket 1 supports one-bank DRAM modules. DIMM sockets 2 and 3 support both one- and two-bank DRAM modules. The PSX custom IC provides memory control for the system RAM. For additional information about supported DRAM, see "DRAM DIMMs" beginning on page 48.

## **Custom ICs**

The architecture of the Apple Logic Board Design LPX-40 is designed around five large custom integrated circuits:

- the PSX memory controller and PCI bridge

- the O'Hare I/O subsystem and DMA engine

- the AWACS sound processor

- the CudaLite ADB controller

- the ATI 264VT-A4S2 graphics controller

The computer also uses several standard ICs that are used in other Macintosh computers. This section describes only the custom ICs.

#### PSX IC

The PSX IC functions as the bridge between the PowerPC 603e or the PowerPC 604e microprocessor and the PCI bus. It provides buffering and address translation from one bus to the other.

The PSX IC also provides the control and timing signals for system cache, ROM, and RAM. The memory control logic supports byte, word, long word, and burst accesses to the system memory. If an access is not aligned to the appropriate address boundary, PSX generates multiple data transfers on the bus.

#### **Memory Control**

The PSX IC controls the system RAM and ROM and provides address multiplexing and refresh signals for the DRAM devices. For information about the address multiplexing, see "RAM Address Multiplexing" on page 53.

#### PCI Bus Bridge

The PSX IC acts as a bridge between the processor bus and the PCI expansion bus, converting signals on one bus to the equivalent signals on the other bus. The PCI bridge functions are performed by two converters. One converter accepts requests from the

processor bus and presents them to the PCI bus. The other converter accepts requests from the PCI bus and provides access to the RAM and ROM on the processor bus.

The PCI bus bridge in the PSX IC runs asynchronously so that the processor bus and the PCI bus can operate at different rates. The processor bus operates at a clock rate of 40 MHz, and the PCI bus operates at 33.33 MHz.

The PCI bus bridge generates PCI parity as required by the PCI bus specification, but it does not check parity or respond to the parity error signal.

#### **Big-Endian and Little-Endian Bus Addressing**

Byte order for addressing on the processor bus is big endian and byte order on the PCI bus is little endian. The bus bridge performs the appropriate byte swapping and address transformations to translate between the two addressing conventions. For more information about the translations between big-endian and little-endian byte order, see Part One, "The PCI Bus," in *Designing PCI Cards and Drivers for Power Macintosh Computers*.

#### **Processor Bus to PCI Bus Transactions**

Transactions from the processor bus to the PCI bus can be either burst or nonburst. Burst transactions are always 32 bytes long and are aligned on cache-line or 8-byte boundaries. In burst transactions, all the bytes are significant. Burst transactions are used by the microprocessor to read and write large memory structures on PCI devices.

#### Note

For the processor to generate PCI burst transactions, the address space must be marked as cacheable. Refer to *Macintosh Technote Number 1008*, *Understanding PCI Bus Performance*, for details. ◆

Nonburst transactions can be of arbitrary length from 1 to 8 bytes and can have any alignment. Nonburst transactions are used by the processor to read and write small data structures on PCI bus devices.

#### PCI Bus to Processor Bus Transactions

For transactions from the PCI bus to the processor bus, the bridge responds only to PCI bus memory commands and configuration commands. On the processor bus, the bridge generates a burst transaction or a nonburst transaction depending on the type of command and the address alignment. For Memory Write and Invalidate commands that are aligned with the cache line, the bridge generates a burst-write transaction. Similarly, for Memory Read Line and Memory Read Multiple commands whose alignment is less than three-quarters through a cache line, the bridge generates a burst-read transaction. The maximum burst-read or burst-write transaction allowed by the bridge is 32 bytes—8 PCI beats.

Commands other than those mentioned here are limited to two beats if aligned to a processor bus doubleword boundary and to one beat otherwise.

### O'Hare IC

The O'Hare IC is based on the Grand Central IC present in the Power Macintosh 7500 computer. It is an I/O controller and DMA engine for Power Macintosh computers using the PCI bus architecture. It provides power-management control functions for energy management features included on the Apple Logic Board Design LPX-40. The O'Hare IC is connected to the PCI bus and uses the 33.33 MHz PCI bus clock.

The O'Hare IC includes circuitry equivalent to the IDE, SCC, SCSI, sound, SWIM3, and VIA controller ICs. The functional blocks in the O'Hare IC include the following:

- support for descriptor-based DMA for I/O devices

- system-wide interrupt handling

- a SWIM3 floppy drive controller

- SCSI controller (MESH based)

- SCC serial I/O controller

- IDE hard disk interface controller

- sound control logic and buffers

The O'Hare IC provides bus interfaces for the following I/O devices:

- CudaLite ADB controller IC (VIA1 and VIA2 registers)

- AWACS sound input and output IC

- 8 KB nonvolatile RAM control

The SCSI controller in the O'Hare IC is a MESH controller. DMA channels in the O'Hare IC are used to support data transfers. The clock signal to the SCSI controller is 45.1584 MHz.

The O'Hare IC also contains the sound control logic and the sound input and output buffers. There are two DMA data buffers—one for sound input and one for sound output—so the computer can record sound input and process sound output simultaneously. The data buffer contains interleaved right and left channel data for support of stereo sound.

The SCC circuitry in the O'Hare IC is an 8-bit device. The PCLK signal to the SCC is a 15.6672 MHz clock (one half of the 33.3344 MHz reference frequency). The SCC circuitry supports GeoPort and LocalTalk protocols.

### AWACS Sound IC

The audio waveform amplifier and converter (AWACS) is a custom IC that combines a waveform amplifier with a 16-bit digital sound encoder and decoder (codec). It conforms to the IT&T *ASCO 2300 Audio-Stereo Codec Specification* and furnishes high-quality sound input and output. For information about the operation of the AWACS IC, see Chapter 3 of *Developer Note: Power Macintosh Computers*, available on the developer CD-ROM and as part of *Macintosh Developer Note Number 8*.

#### CudaLite IC

The CudaLite IC is a custom version of the Motorola MC68HC05 microcontroller. It provides several system functions, including

- the ADB interface

- PS2 keyboard and mouse interface

- management of system resets

- management of the real-time clock

- on/off control of the power supply (soft power)

#### ATI 264VT-A4S2 IC

The ATI 264VT-A4S2 IC is a custom IC containing the logic for the video display. It includes the following functions:

- display memory controller, clock generator, and video DAC (digital-to-analog converter)

- video CLUT (color lookup table)

- 2D graphics acceleration

- true color palette DAC supporting pixel clock rates to 135 MHz for 1280-by-1024 resolution at 75 Hz

- hardware cursor up to 64x64x2

- DCC1 and DDC2B plug-and-play monitor support

- supports EDO DRAM up to 60 MHz memory clock across a 64-bit memory interface

- supports SDRAM or SGRAM up to 80 MHz memory clock, providing a bandwidth up to 640 MB per second

A separate data bus handles data transfers between the ATI 264VT-A4S2 IC and the display memory. The display memory data bus is 64 bits wide for display memory of 2 MB or greater. For 1 MB of display memory, the data bus is 32 bits wide. The ATI 264VT-A4S2 IC breaks each 64-bit data transfer into several pixels of the appropriate size for the current display mode—4, 8, 16, 24, or 32 bits per pixel.

The ATI 264VT-A4S2 IC has an internal phase locked loop (PLL) to generate clocks for the display memory interface and the pixel digital to analog converter (DAC).

The 2D graphics accelerator is a fixed-function accelerator for rectangle fill, line draw, polygon fill, panning/scrolling, bit masking, monochrome expansion, and scissoring with full ROP support.

## Display RAM DIMM

The display memory is separate from the main memory. The Apple Logic Board Design LPX-40 supports +5 V EDO DRAM, +3.3 V SDRAM and +3.3 V SGRAM devices for

video memory expansion. The video memory DIMM can be configured as 1 MB, 2 MB, or 4 MB.

The maximum supported size for an EDO video DIMM is 2 MB. EDO video DIMMs larger than 2 MB provide no additional performance due to the limited bandwidth of the EDO devices.

With a 4 MB SGRAM DIMM, the display data generated by the computer can have pixel depths of 4, 8, 16, 24, or 32 bits for monitors up to 1024-by-768 pixels and 4, 8, or 16 bits for larger monitors up to 1280-by-1024 pixels.

For additional information about video on the Apple Logic Board Design LPX-40, see "Built-in Video" on page 38 and "Video RAM" on page 58.

# I/O Features

I/O Features

This chapter describes both the built-in I/O devices and the interfaces for external I/O devices. It also describes the types of external video monitors that can be used with the Apple Logic Board Design LPX-40.

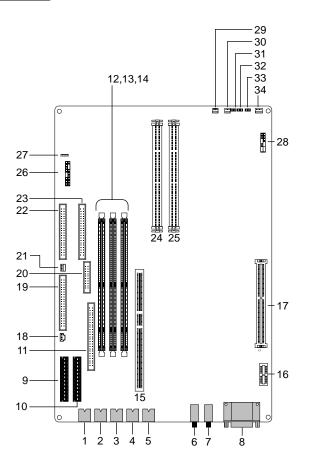

# Board Layout

The Apple Logic Board Design LPX-40 is built to the industry standard LPX 13-by-9 inch form factor and can be installed in many off-the-shelf low profile and tower enclosures. The layout of the connectors on the board is shown in Figure 3-1.

#### Figure 3-1 App

Apple Logic Board Design LPX-40 connector layout

#### I/O Features

Table 3-1 lists the locations and types of connectors on the Apple Logic Board Design LPX-40. Refer to the connector numbers in Figure 3-1 to determine the location of each connector on the logic board.

| Table 3-1 | Connectors on the Apple Logic Board Design LPX-40 |                                    |  |

|-----------|---------------------------------------------------|------------------------------------|--|

| Location  | Description                                       | Connector type                     |  |

| 1         | PS/2 mouse port                                   | 6-pin mini-DIN                     |  |

| 2         | PS/2 keyboard port                                | 6-pin mini-DIN                     |  |

| 3         | Apple ADB port                                    | 4-pin mini-DIN                     |  |

| 4         | Apple printer serial port                         | 9-pin mini-DIN                     |  |

| 5         | Apple modem serial port                           | 9-pin mini-DIN                     |  |

| 6         | Sound in                                          | Mini-phono jack                    |  |

| 7         | Sound out                                         | Mini-phono jack                    |  |

| 8         | Monitor out                                       | 15-pin Macintosh or SVGA connector |  |

| 9         | Power supply                                      | 12-pin header                      |  |

| 10        | Power supply                                      | 12-pin header                      |  |

| 11        | SCSI                                              | 50-pin header                      |  |

| 12        | DRAM DIMM slot 3                                  | 168-pin connector                  |  |

| 13        | DRAM DIMM slot 2                                  | 168-pin connector                  |  |

| 14        | DRAM DIMM slot 1                                  | 168-pin connector                  |  |

| 15        | PCI riser connector                               | 192-pin connector                  |  |

| 16        | GIMO                                              | 22-pin connector                   |  |

| 17        | Video DIMM                                        | 120-pin connector                  |  |

| 18        | Power supply soft power                           | 3-pin header                       |  |

| 19        | MFM floppy disk drive                             | 34-pin header                      |  |

| 20        | Apple GCR floppy disk drive                       | 20-pin header                      |  |

| 21        | CD-audio                                          | 4-pin header                       |  |

| 22        | ATAPI CD-ROM                                      | 40-pin header                      |  |

| 23        | ATA (IDE) hard disk                               | 40-pin header                      |  |

| 24        | ROM connector                                     | 160-pin connector                  |  |

| 25        | L2 cache connector                                | 160-pin connector                  |  |

| 26        | Feature options jumper                            | (6) 3-pin headers                  |  |

| 27        | Battery connector                                 | 4-pin header                       |  |

continued

| Location | Description                          | Connector type    | _ |  |

|----------|--------------------------------------|-------------------|---|--|

| 28       | CPU frequency multiplier<br>(jumper) | (4) 3-pin headers |   |  |

| 29       | Fan                                  | 3-pin header      |   |  |

| 30       | Power LED                            | 3-pin header      |   |  |

| 31       | Reset switch                         | 2-pin header      |   |  |

| 32       | Soft power switch                    | 2-pin header      |   |  |

| 33       | NMI switch                           | 2-pin header      |   |  |

| 34       | Speaker                              | 4-pin header      |   |  |

#### Table 3-1 Connectors on the Apple Logic Board Design LPX-40 (continued)

## Serial I/O Ports

The Apple Logic Board Design LPX-40 supports four serial ports: two 9-pin mini-DIN serial ports for a printer and a modem and two PS/2 serial ports for a PS/2 keyboard and mouse. The PS/2 ports are strictly for a PS/2 keyboard and mouse and are not general purpose serial I/O channels.

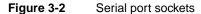

## Apple Printer and Modem Ports

The printer and modem serial ports have 9-pin mini-DIN sockets that accept either 8-pin or 9-pin plugs. Both ports support LocalTalk and GeoPort serial protocols. Figure 3-2 shows the mechanical arrangement of the pins on the serial port sockets; Table 3-2 shows the signal assignments.

| Pin | Signal name | Signal description                                          |

|-----|-------------|-------------------------------------------------------------|

| 1   | HSKo        | Handshake output                                            |

| 2   | HSKi        | Handshake input (external clock on modem port)              |

| 3   | TxD-        | Transmit data –                                             |

| 4   | GND         | Ground                                                      |

| 5   | RxD-        | Receive data –                                              |

| 6   | TxD+        | Transmit data +                                             |

| 7   | GPi         | General-purpose input (wakeup CPU or perform DMA handshake) |

| 8   | RxD+        | Receive data +                                              |

| 9   | +5 V        | +5 volts to external device (100 mA maximum)                |

#### Note

Pin 9 on each serial connector provides +5 V power for external devices. The total current available for all devices connected to the +5 V pins on the serial ports, PS/2 ports, and ADB ports is 500 mA. Each external device should draw no more than 100 mA. Excessive current drain will cause a fuse to interrupt the +5 V supply; the fuse automatically resets when the load returns to normal.  $\blacklozenge$

Both serial ports include the GPi (general-purpose input) signal on pin 7. The GPi signal for each port connects to the corresponding data carrier detect input on the SCC portion of the O'Hare custom IC, described in Chapter 2. On both serial ports, the GPi line can be connected to the receive/transmit clock (RTxCA) signal on the SCC. That connection supports devices that provide separate transmit and receive data clocks, such as synchronous modems. For more information about the serial ports, see *Guide to the Macintosh Family Hardware*, second edition.

# PS/2 Keyboard and Mouse Ports

The Apple Logic Board Design LPX-40 provides two 6-pin mini-DIN PS/2 ports for connection of a PS/2 keyboard and PS/2 mouse. Table 3-3 lists the pin assignments for the PS/2 ports.

| Table 3-3 | PS/2 port signals |                         |

|-----------|-------------------|-------------------------|

| Pin       | Signal name       | Description             |

| 1         | Data              | Bidirectional data      |

| 2         | n.c.              | Not connected           |

| 3         | GND               | Ground                  |

| 4         | +5 V              | +5 V to external device |

| 5         | Clock             | Bidirectional clock     |

| 6         | n.c.              | Not connected           |

|           |                   |                         |

The PS/2 serial port implementation on the Apple Logic Board Design LPX-40 does not support all permutations of PS/2 keyboards and mouse devices. In particular, only two-button mouse devices that generate a 1 in the sync bit position (bit 3 of the first data byte) of the protocol are supported and only AT-type keyboards are supported. PC keyboards that implement XT or RT key codes are not supported.

The CudaLite custom IC implements a translation layer that converts the PS/2 device protocols to ADB protocol so that no system ROM or system software changes are required to support PS/2 devices. Because the translation layer is resident within the masked firmware, only a fixed set of PS/2 devices are supported. There is no mechanism for providing translation for alternate PS/2 input devices.

Translation of AT key codes to Macintosh key codes is dependent on the ADB handler ID that is assigned to the keyboard. When the ADB handler ID for the PS/2 keyboard is set to 0x02, translation emulates an ADB extended keyboard with ADB handler ID 0x02, where left and right modifier keys (option, control or shift) return the same Macintosh key codes to the host CPU. When the ADB handler ID for the PS/2 keyboard is set to 0x03, translation emulates an ADB extended keyboard with ADB handler ID 0x03, where left and right modifier keys (option, control, or shift) return unique Macintosh key codes to the host CPU.

The AT keyboard to Macintosh keyboard key maps and key codes for the ID=2 AT key code translation ADB handler are shown in Figure 3-3.

#### Note

The PS/2 serial ports are strictly for a PS/2 keyboard and mouse. Other devices are not supported on the ports.  $\blacklozenge$

Figure 3-3 ADB handler ID=2 key maps and key codes

| AT Mode Key Map                                     |               |   |    |              |  |  |  |  |  |  |

|-----------------------------------------------------|---------------|---|----|--------------|--|--|--|--|--|--|

| Esc F1F2F3F4 F5F6F7F8 F9F10F11F12 Print ScrLk Pause |               |   |    |              |  |  |  |  |  |  |

|                                                     | Cle           |   | *  | _            |  |  |  |  |  |  |

| TAB O W E R T Y U I O P [ ] . Del End PgDp          | 5             | 6 | 0  | +            |  |  |  |  |  |  |

|                                                     | 4             | 5 | ÷, | Ċ            |  |  |  |  |  |  |

|                                                     | $\frac{1}{1}$ | 5 | 3  | <del>ک</del> |  |  |  |  |  |  |

| Ctriling Alt Space Alt in Electril + + +            | 1 di          | - | Ť  | ŧ            |  |  |  |  |  |  |

| AT Mode Key Codes                         |    |    |    |    |    |    |    |

|-------------------------------------------|----|----|----|----|----|----|----|

| 76 0506040C 0308830A 01097807             | 84 | 7E |    |    |    |    |    |

| 0E 16 1E 26 25 2E 36 3D 3E 46 45 4E 55 66 | 70 | 6C | 7D | 77 | 4A | 70 | 7B |

| 0D 15 1D 24 2D 2C 35 3C 43 44 4D 54 5B    | 71 | 69 | 78 | 6C | 75 | 7D |    |

| 58 1C 18 23 28 34 33 38 42 48 4C 52 5A    |    |    |    | 6B | 73 | 74 | 79 |

| 12 18 22 21 28 32 31 38 41 49 48 59 5D    |    | 75 |    | 69 | 72 | 78 |    |

| 14 1F 11 29 11 27 2F 14                   | 6B | 72 | 74 | 7  | 0  | 71 | 5A |

#### Macintosh Key Codes

35 78 78 63 76 60 61 62 64 65 60 67 6F 69 68 71

| 32 12 13 14 | 15 17 16 1A 1C 1 | 19 1D 1B 18 33 | 72 73 74 | 47 48 43 4E |

|-------------|------------------|----------------|----------|-------------|